Si vais siguiendo mis artículos, en particular este, conoceréis la nueva arquitectura de cachés que ha introducido Intel en sus nuevos procesadores Sandy Bridge. En particular, Intel ha aumentado de forma crítica el ancho de banda de las cachés L1 y L2 para alimentar correctamente a los potenciados núcleos de ejecución de enteros (INT ALU 64 bit, MMX ALU 64 bit y SSE 128 bit) y de coma flotante (X87 FPU 64 bit, SSE 128 bit y AVX de 256 bit).

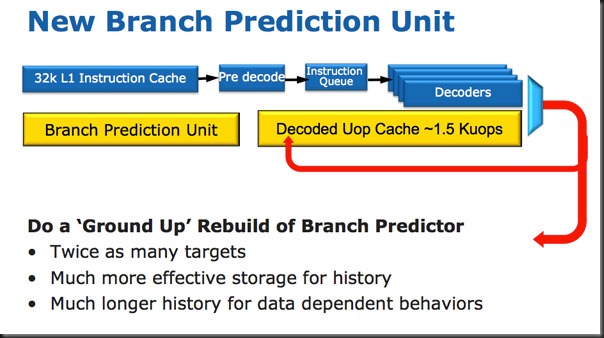

El segundo cambio consiste en la creación de un nuevo nivel de caché de instrucciones previo a la L1i de 32 KB y 8 vías (8 ways associativity). Para ello Intel ha dotado a Sandy Bridge de una caché L0i de modesto tamaño (unas 1500 micro ops según Intel) con una tasa de aciertos efectiva sobre el 80%.

Ya traté en cierta extensión esta nueva caché L0i junto con un análisis pormenorizado de la caché L3 multibanco de 8 MB en el siguiente artículo de LowLevelHardware: Intel Core i7 2600 K. Análisis cachés L0i 6 KB y L3 unificada 8 MB – LowLevelHardware

Hay cuatro motivaciones principales para este profundo rediseño:

En primer lugar reducir el uso de los X86 decoders: y gracias a ello el consumo energético de estas gigantescas estructuras diseñadas para traducir las complejas instrucciones X86 a micro instrucciones al estilo RISC.

Como sabéis los X86 decoders tienen un gran tamaño físico consumiendo un gran número de transistores y por ello una disipación térmica muy alta. Intel, al crear un nuevo nivel de caché de instrucciones previo al nivel 1, un nivel 0 en la práctica, se permite desactivar los decoders cuando se da un L0i hit (acierto de la micro op cache).

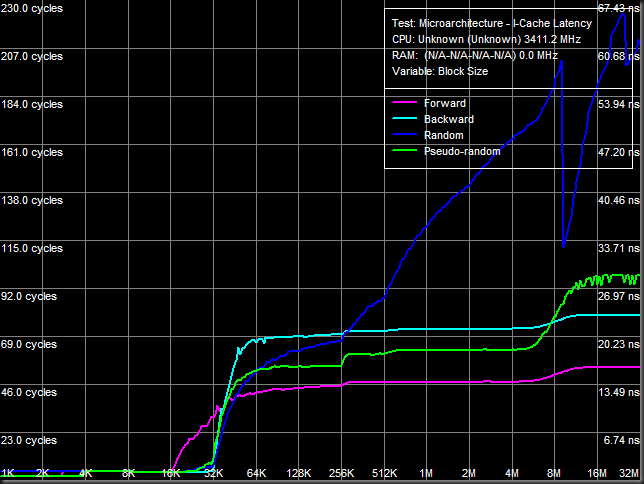

Instruction cache: la L0i obtiene una increíble latencia de 2 ciclos (zona 0 – 4 KB).

Instruction cache: la L0i obtiene una increíble latencia de 2 ciclos (zona 0 – 4 KB).

Un segundo motivo es reducir la latencia media en peticiones a la caché L1i. La L0i micro op cache contiene instrucciones decodificadas, se encuentra tras los decoders y trabaja en paralelo con el resto de los pipelines de ejecución. En caso de que una secuencia de instrucciones se encuentre en la L0i (un L0i hit) Intel desactiva(obviamente según un algoritmo optimizado) la circuitería de decodificación X86 del procesador y además como beneficio obtenemos una latencia reducida como demostré en un artículo anterior.

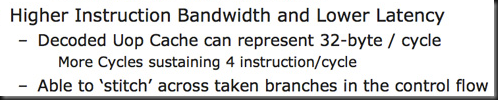

En tercer lugar aumentar el ancho de banda medio de fetching de instrucciones. La L1i no es capaz de transmitir 32 bytes por ciclo de modo sostenido, en cambio en caso de un L0i hit la micro op cache si lo consigue aumentando el uso de las unidades de ejecución:

Intel Sandy Bridge SUB decode bandwidth.

Intel Sandy Bridge SUB decode bandwidth.

La micro op cache también mejora las latencias medias en caso de branch Misprediction.

La micro op cache también mejora las latencias medias en caso de branch Misprediction.

Y por último reducir la longitud efectiva de los pipelines de ejecución. En caso de un L0i hit el pipeline empieza en la práctica desde la micro op cache reduciéndose en un número importante de etapas. Se consigue por ello una importante reducción en la penalización por Branch Misprediction (fallo de predicción de branches) en caso de darse un L0i hit.

Resultados de los tests. Bandwidth decode:

En este artículo presento resultados experimentales que avalan los hechos que acabo de detallar y ensalzan el excelente diseño conseguido por los ingenieros de Intel en esta gama de procesadores.

Todos los análisis se han realizado en un sistema Sandy bridge Core i7 2600K con Turbo Mode desactivado para evitar incorrecciones de medida y Windows XP Professional X64 SP2 con todas las actualizaciones al día y los últimos drivers para el chipset P67. Por cierto, las pruebas se han realizado en un stepping B1 del chipset y por ello libre del infame SATA2 bug.

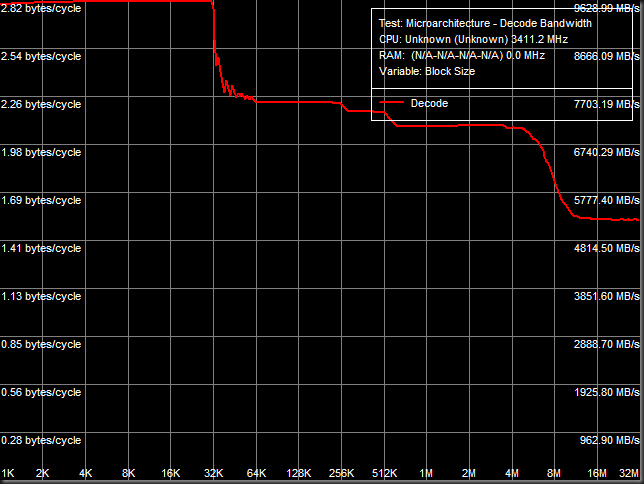

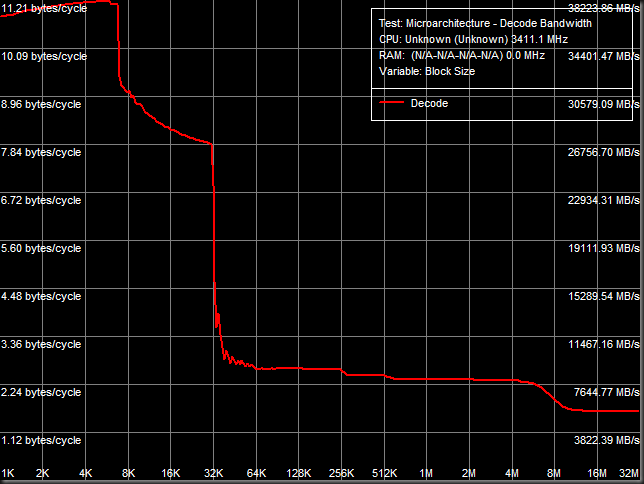

Para aclarar conceptos, voy a mostrar un gráfico de ancho de banda de decodificación típico en un procesador convencional (sin micro op cache) por ejemplo un Intel Nehalem:

Decode bandwidth en Intel Nehalem.

Decode bandwidth en Intel Nehalem.

Esta gráfica la obtuve en Noviembre de 2008 probando los primeros Intel Core i7 920 stepping C0/C1 comerciales semanas antes de salir al mercado.

Observamos cuatro zonas con valores en bytes/ciclo claramente diferenciados:

- Zona 1: Caché L1i de 32 KB, desde los 1 – 32 KB.

- Zona 2: Caché L2 unificada de 256 KB, desde los 32 a los 256 KB.

- Zona 3: Caché L3 compartida de 8 MB, desde los 256 KB a los 8 MB.

- Zona 4: Memoria RAM, de los 8 MB en adelante. Tened en cuenta que entonces probé el sistema con un dual channel DDR3 1333 (no tenía a mi alcance 3 DIMM DDR3 con voltaje de sólo 1.65V).

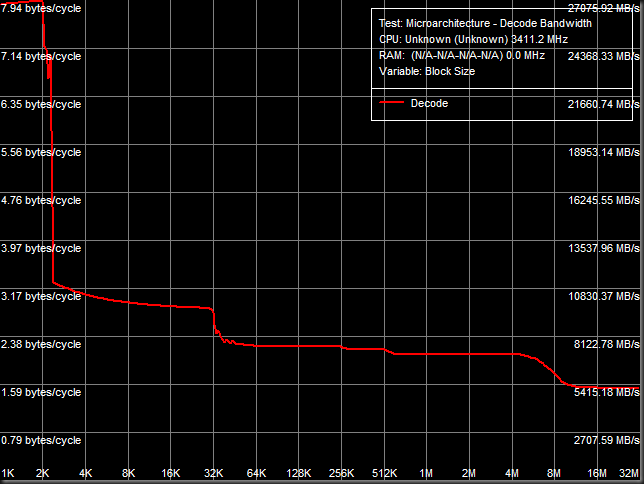

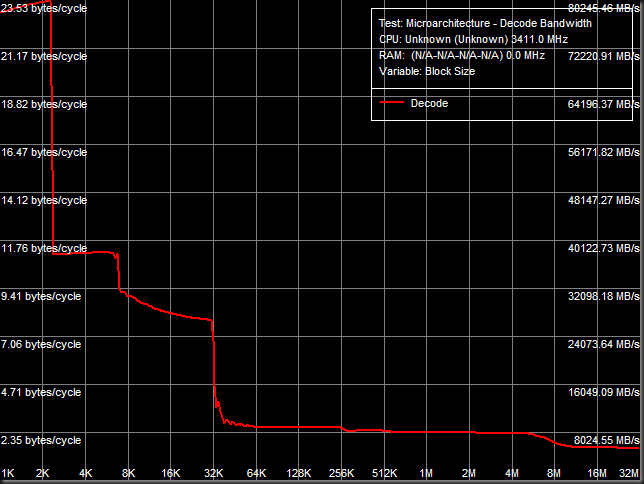

Ahora veamos los resultados típicos de un core Sandy Bridge:

Observamos cinco zonas con valores en bytes/ciclo claramente diferenciados:

- Zona 1. Caché L0i micro op cache. En este caso su tamaño efectivo es de unos 2 KB. Es una caché inclusiva como es tradición en los diseños de Intel.

- Zona 2: Caché L1i de 32 KB, desde los 2 – 32 KB.

- Zona 3: Caché L2 unificada de 256 KB, desde los 32 a los 256 KB.

- Zona 4: Caché L3 compartida de 8 MB, desde los 256 KB a los 8 MB.

- Zona 5: Memoria RAM, de los 8 MB en adelante.

En primer lugar debo decir que he observado varias peculiaridades en el funcionamiento de este nuevo nivel de caché:

- No todos los tipos de instrucciones son aparentemente cacheadas en la micro op cache. Por ejemplo, algunas instrucciones como Test son decodificadas cada vez que son encontradas en el flujo de instrucciones y las mediciones indican que son enviadas desde la L1i como en diseños anteriores:

Intel Sandy Bridge: Test decode bandwidth.

Intel Sandy Bridge: Test decode bandwidth.

Observamos que no hay ningún incremento de velocidad de decodificación en la zona de 1 – 6 KB, la micro op caché no cachea estas instrucciones.

- En cambio, en otros casos muestra una asombrosa eficacia multiplicando por más de 2 los resultados en ancho de banda de la L1i:

Intel Sandy Bridge: Prefixed CMP decode bandwidth.

Intel Sandy Bridge: Prefixed CMP decode bandwidth.

Si os fijáis, el tamaño efectivo medido en estos tests sitúa a la L0i sobre los 2 – 2.5 KB. En otros tests en cambio podemos llegar hasta los 6 KB, que es el tamaño “publicitado” por Intel:

Intel Sandy Bridge: Prefixed CMP4 decode bandwidth.

Intel Sandy Bridge: Prefixed CMP4 decode bandwidth.

Con instrucciones ALU Prefixed CMP4 llegamos hasta un tamaño efectivo para la micro op cache de unos 6 – 7 KB.

Conclusiones:

El diseño de un procesador actual comprende numerosos equipos diferentes trabajando en aspectos separados del diseño final. El arquitecto jefe diseña el plan general y los objetivos que debe de cumplir el nuevo producto.

Uno de los factores limitantes para el diseño de cada unidad del procesador es la superficie que ocupa. A cada una unidad se le asignan unos milímetros cuadrados (o fracciones de mm2) e incluso una morfología determinada por necesidades espaciales de unidades adyacentes.

Otra limitación reside en el consumo en reposo (idle) conocido como leakage (filtrado de corriente con los transistores en off) y en carga típica (TDP) y máxima de cada unidad del diseño. También ahí se imponen graves y rígidas restricciones.

Este último factor ha motivado la inclusión de Register Files y también de la micro op caché en Sandy Bridge, ambos persiguen un solo objetivo: una importante reducción del consumo. Todo ello motivado por la inclusión en el die de la GPU integrada, el hardware de coding – decoding de video y las nuevas unidades de proceso FPU de 256 bit AVX.

Si te gusta la cosmología o la astronomía echa un vistazo a mi artículo sobre Estructura a gran escala del universo en IdeasYCiencia.

Si consideras útil el contenido de este Blog, ayuda a mantenerlo ojeando algunas de las ofertas que consideres interesantes de nuestros anunciantes.

![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://lh3.googleusercontent.com/-kHlUuqbY4vU/WJNS5bWiutI/AAAAAAAAK5Q/df4W8vyaSV4/informaticapremium-logo-150px%25255B3%25255D%25255B2%25255D.png?imgmax=800)

No hay comentarios:

Publicar un comentario

Nota: solo los miembros de este blog pueden publicar comentarios.